# Investing the Effectiveness of Retention Performance in a Non-Volatile Floating Gate Memory Device with a Core-Shell Structure of CdSe Nanoparticles

Dong-Hoon Lee,<sup>1,†</sup> Jung-Min Kim,<sup>2,†</sup> Ki-Tae Lim,<sup>1</sup> Hyeong Jun Cho,<sup>1</sup> Jin Ho Bang,<sup>3</sup> and Yong-Sang Kim<sup>1,\*</sup>

<sup>1</sup>School of Electronic and Electrical Engineering, Sungkyunkwan University, Suwon 440-746, Korea <sup>2</sup>Materials & Devices Lab., Corporate R&D Institute, Samsung Electro-Mechanics Co. Ltd.,

Suwon 443-743, Korea

<sup>3</sup>Department of Chemistry and Applied Chemistry, Hanyang University, Ansan 426-791, Korea

(received date: 21 October 2015 / accepted date: 4 January 2016 / published date: 10 March 2016)

In this paper, we empirically investigate the retention performance of organic non-volatile floating gate memory devices with CdSe nanoparticles (NPs) as charge trapping elements. Core-structured CdSe NPs or core-shell-structured ZnS/CdSe NPs were mixed in PMMA and their performance in pentacene based device was compared. The NPs and self-organized thin tunneling PMMA inside the devices exhibited hysteresis by trapping hole during capacitance-voltage characterization. Despite of core-structured NPs showing a larger memory window, the retention time was too short to be adopted by an industry. By contrast core-shell structured NPs showed an improved retention time of >10000 seconds than core-structure NCs. Based on these results and the energy band structure, we propose the retention mechanism of each NPs. This investigation of retention performance provides a comparative and systematic study of the charging/discharging behaviors of NPs based memory devices.

### **1. INTRODUCTION**

As the use of flexible electronic devices such as medical diagnostic devices, wearable devices and radio frequency identification (RFID) tags has increased explosively, extensive effort is being made for development of a non-volatile memory having high density and low cost with considerable retention time (>10 years).<sup>[1-7]</sup> Amongst the many types of non-volatile memory, flash memory, which uses a floating gate layer in a field effect transistor (FET) as a charge-trapper, is the most widely used.<sup>[8-11]</sup> Typically, the floating gate is a charge trapping site, which acts as the storage unit surrounded by SiO<sub>2</sub> resistive barriers. These barriers prevent

carrier escape, so that the charge contained in the floating gate remains unchanged for long periods. However, despite good performance, an inorganic layer is not suitable for use in disposable and flexible electronics due to its high processing cost and brittleness. To improve device flexibility and decrease process cost, the recent trend for flash memory devices is to store information in discrete charge trapping sites using nanocrystals (NCs) with an organic insulator.<sup>[12,13]</sup>

Among various NCs, nanoparticles (NPs) are promising candidates due to easier synthesis and growth than other shapes. For this reason, many researchers have investigated various NPs, such as Cr,<sup>[14]</sup> Ag,<sup>[15]</sup> and Au,<sup>[16]</sup> in a floating-gate structure. Lee *et al*.<sup>[17]</sup> reported that the trap density of the floating gate can be controlled by accumulating Au NPs with layer-by-layer assembly. More recently, they showed that tunable memory characteristics can be obtained by using metal NPs with different electron affinities and a binary

<sup>&</sup>lt;sup>†</sup>These authors contributed equally to this work

<sup>\*</sup>Corresponding author: yongsang@skku.edu

<sup>©</sup>KIM and Springer

mixture of metal NPs. Along with these elemental metallic NPs, CdSe NPs are also promising because of their unique quantum phenomena at room temperature. While the devices based on metallic NPs have just a few fixed bandoffsets, depending on the work function of the metal element, the properties of CdSe NPs are flexible. As CdSe possesses size-tunable electronic and optical properties resulting from quantum confinement, memory characteristics can be controlled based on their structure and sizes. A few studies have reported memory devices incorporating NPs to have many intriguing properties.<sup>[18,19]</sup> Unfortunately, despite the fact that organic materials have lower program/erase voltage, less damage, great endurance for write/erase cycles, and improved reliability; the retention time, an important property, was not up to the mark.<sup>[20,21]</sup> Therefore, various device structures incorporating NCs mixed with an organic material or multilayered devices have been suggested and investigated to improve retention performance.

For this reason, in this paper, we investigated the retention performance of organic non-volatile floating-gate memory devices using core-structure CdSe NPs of varying size and core-shell structure CdSe NPs. We established a retention mechanism by analyzing the energy-band structure of the device.

#### 2. EXPERIMENTAL PROCEDURE

We fabricated the organic memory using a solution process in which CdSe NPs with different sizes and structures were employed as charge-trapping elements. The unique feature of this study is that a multilayer of self-organized CdSe NPs were formed inside the polymethylmethacrylate (PMMA) tunneling insulator, which provides a large memory window and potential multilevel charging characteristics. A distinct dependency and variation of memory characteristics on the size of CdSe NPs was observed. A wider memory window and larger charge trapping were achieved with increasing NP size.

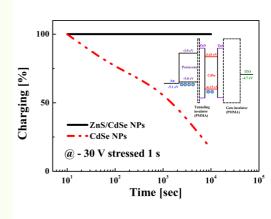

Figure 1(a) shows a schematic illustration of the organic memory device, which comprises CdSe NPs under the pentacene layer. The metal-insulator-semiconductor (MIS) structure was fabricated on an indium-tin-oxide (ITO) coated conventional glass substrate. Firstly, a control device without CdSe NPs was fabricated by spin-coating PMMA solution on the ITO surface. The device was then baked at 160°C in a conventional oven for crystallization of PMMA insulator, which results in a 400-nm-thick PMMA insulating layer. A pentacene active layer (thickness of 70 nm) and gold top electrode was subsequently deposited on the PMMA surface using thermal evaporation. To fabricate an NP-based floating gate memory device, a mixed solution of CdSe NPs and PMMA was spin-coated on the PMMA layer. The film was baked in the oven, resulting in a NPs layer (50 nm) with

**Fig. 1.** (a) Schematic of the bottom-gate memory device structure using a CdSe NPs + PMMA blend as the tunneling layer for non-volatile organic memory, and (b) cross-sectional STEM image of the fabricated device featuring CdSe NPs embedded in PMMA layer.

a thin PMMA layer (25 nm), and then the semiconductor and Au electrode were serially deposited.

In this study, four types of NP differing in size distributions and structures were used: i) three core-structured CdSe NPs of 2.8, 3.3, and 4.0 nm diameter with trioctylphosphineoxide (TOPO) stabilizer were used to investigate the size effect on memory performance, and ii) a core-shell structured ZnS/ CdSe NPs of ZnS capping shell was used to study the effect of structure. Figure 1(b) shows a cross-sectional scanning transmission electron microscopy (STEM) image of the fabricated device, indicating that CdSe NPs were uniformly embedded in PMMA layers without any aggregation during the blending process.

## 3. RESULTS AND DISCUSSION

These memory devices are based on charge-carrier transfer from the pentacene active layer to the NP layer. The transferred carriers are trapped in the NPs, resulting in individual charged islands inside the device, which consequently exhibits hysteresis behavior in capacitance-voltage (C-V). The thick PMMA layer is used to prevent the transfer of the charges between the ITO gate and the charge-trapping layer during charging/discharging operations. Therefore, the "programmed" state refers to the transfer of charge carriers (hole) from the pentacene layer to NPs upon negative bias on the gate, and the reverse operation is called the 'erased' state, in which the charge stored in the NPs is moved to the pentacene when a positive bias is applied. The programmed and erased states can be determined by the C-V characteristics upon application of bias voltage.

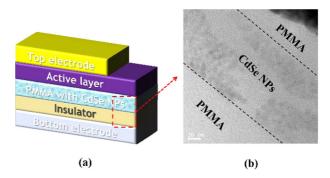

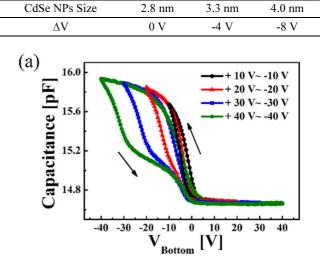

Figure 2(b) shows the C-V curves at 100 kHz for the device with respect to the size distribution of CdSe NPs. While the control device without CdSe NPs showed no hysteresis (Fig. 2(a)), the devices comprising CdSe NPs clearly displayed a hysteresis loop in a counter-clockwise direction upon sweeping the applied voltage at the bottom

**Fig. 2.** The C-V characteristic of the fabricated organic memory device at different sweeping range (a) without CdSe NPs and (b) with respect to the size of CdSe NPs.

electrode between +40 and -40 V (Fig. 2(b). This indicated that a significant density of charge trapping sites exists inside the PMMA layer (and/or its interface), whereas it is negligible in the absence of NPs. The observed hysteresis during cyclic voltage sweeping was caused by the charging of CdSe NPs.

The C-V curve appeared to shift in the negative direction, indicating that the NPs layer was charged by holes due to a negative voltage. It is of importance that a greater hysteresis was clearly observed upon increasing the size of the NPs. The size-dependent capacitance of NPs can be expressed as  $C_{sp}(r) = 4\pi\varepsilon_o\varepsilon_r r^2$ , where  $\varepsilon_o$  is the vacuum permittivity,  $\vartheta r$  is the dielectric constant of the material surrounding the particle, and r is the radius of the NPs.<sup>[21]</sup> Therefore, the greater the size of NPs, the larger is the shift in flat band voltage, resulting in the increasing hysteresis in the C-V curve.

We analyzed the charging/discharging effects of various bias shifts in the C-V curve using CdSe NPs of different sizes as a function of amplitude of the applied positive or negative gate voltage stress. The charging/discharging effects shifted in the negative direction when a bias of -20 and -30 V was applied for 1 s. On the other hand, it shifted slightly in positive direction after erasing the memory by applying a bias of +40 V for 1 s. To evaluate size-dependent performance, memory window ( $\Delta V$ ), which means the difference in the critical voltage between the programmed and erased state, was measured after voltage application. Table 1 shows that the result of  $\Delta V$  for the devices with 4.0, 3.3 and 2.8 nm CdSe NPs are approximately -8, -4 and 0 V at an applied voltage of -30 V, respectively. Upon applying a negative voltage, the resultant negative  $\Delta V$  was attributed to the positive charge of CdSe NPs. The  $\Delta V$  for the device with 4.0 nm CdSe NPs was highest due to the coulomb blockade effect. Coulomb blockade is caused by excessive charging energy  $(W_c)$ , which increases as the size of nanocrystals decreases  $(W_c = e^2/2C_{sp} \text{ and } C_{sp} = 4\pi \varepsilon_0 \varepsilon_r r^2)$ . When  $W_c >> kT$ , thermal energy is no longer sufficient to overcome excessive

Table 1. Charging/discharging memory window of memory device with respect to the size of CdSe NPs.

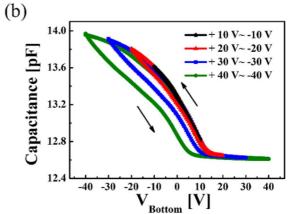

**Fig. 3.** The C-V characteristic of the fabricated organic memory device (a) with CdSe NPs and (b) ZnS/CdSe NPs.

Electron. Mater. Lett. Vol. 12, No. 2 (2016)

(a)

charging energy. The next charge may need to occupy higher level of energy; therefore, the  $\Delta V$  for the device with 4.0 nm CdSe NPs is highest among all of the devices.

The charge density Q in CdSe NPs can be estimated from  $Q = C\Delta V$ , where C is the capacitance between the gate and the CdSe NPs. Assuming all CdSe NPs are in the midst of PMMA layer, the charge density Q in 4.0 nm CdSe NPs can be calculated as the total charge occupied at individual CdSe NPs is  $2.2 \times 10^{11}$  and  $4.3 \times 10^{11}$  ea/cm<sup>2</sup> at applied voltages of -20 and -30 V, respectively.

To investigate the retention performance based on the structural effect of NPs, we additionally fabricated a memory device composed of core-shell structured ZnS/CdSe, and studied its electrical characteristics. ZnS, which covers the surround of CdSe, has a higher band gap than CdSe, resulting in the passivation of its surface. In principle, NPs passivated with inorganic shells exhibit improved tolerance to mechanical processing as well as greater optoelectronic properties. Figure 3 shows C-V curves at 100 kHz for the devices with CdSe NPs and ZnS/CdSe NPs during applied voltage sweeping. The size of the NPs used in this analysis was 4 nm. As shown in Fig. 3(a) and (b), a large hysteresis is

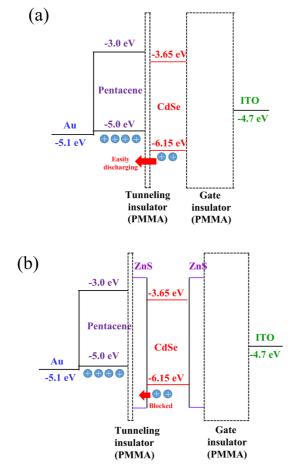

observable in CdSe NPs with the same sweeping range, indicating that the shell of the ZnS/CdSe NPs reduces the hole-charging capability in the device. Figures 4(a) and (b) describe the energy band structure of the device with CdSe and ZnS/CdSe NPs and their accordant charging mechanism. When a sufficiently large electric field is applied (negative bias), holes can tunnel into the valence band of the CdSe NPs from the highest occupied molecular orbital (HOMO) levels of the nearby pentacene molecules. After the negative bias is removed, the tunneled holes are confined in the CdSe NPs (Fig. 4(a)). As shown in Fig. 4(b), holes are difficult to capture in the CdSe due to the energy barrier of the ZnS shell, and so the probability of the electron tunneling from the pentacene molecule to the conduction band of the CdSe NPs is decreased. The number of holes captured in the ZnS/ CdSe NPs decreases due to the lower holes tunneling probability, resulting in a relatively small hysteresis in the C-V curve at the same voltage sweep.

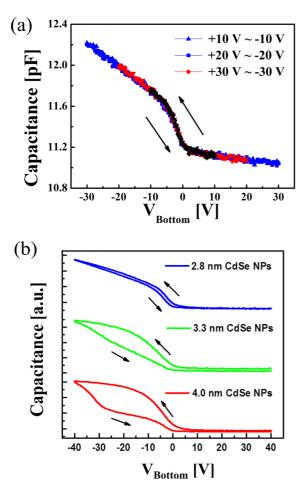

Though the ZnS shell obstacles the hole trapping of the NPs from the pentacene layer, the large band-gap of ZnS can boost the retention of stored charge in the NPs. Charge retention characteristics of the devices with CdSe and ZnS/

Initial After1s Capacitance [pF] 15. After10s After100s 14.9 After1000s After10000s essed at -30V, 2s 14.8 14 0 -2 -1 [V]Bottom (b) 13.7 13.6 Capacitance [pF] Initial 13.5 After1s After10s 13.4 After100s 13.3 After1000s After10000s 13.2 13.1 @stressed at -30V, 1s 13.0 12.9 -2 -1 0 [V]Bottom

**Fig. 4.** The energy band schematic of memory device with (a) CdSE NPs and (b) ZnS/CdSe NPs.

**Fig. 5.** Retention characteristics after applying -30 V voltage stress at the bottom electrode for 1 s: (a) CdSe NP-based device and (b) ZnS/CdSe NP-based device.

Electron. Mater. Lett. Vol. 12, No. 2 (2016)

CdSe NPs were comparably measured from time-dependent capacitance change after programming at room temperature (Fig. 5(a) and (b)). After programming the device at a voltage of -30 V for 1 s, the change in the capacitance ( $\Delta C$ ) was measured at V = 0 V during sweeping V from 2 to -2 V. This measuring procedure minimizes the read disturbance. The retention performance of the device with ZnS/CdSe NPs is better than that with CdSe NPs. The capacitance of the device with CdSe NPs was 14.7 pF after programming, which changed slightly after 103 s. However, the capacitance of the device with ZnS/CdSe NPs after programming showed no significant change even after  $10^4$  s. The ZnS shell acted as a blocking layer for the charge dispersion.

#### 4. CONCLUSIONS

In summary, we investigated the effects of CdSe NPs size and shell on the performance of a non-volatile organic memory device. The memory window ( $\Delta V$ ) widened with increasing size of the CdSe NPs. The charge retention characteristics of the device with the ZnS/CdSe NPs was clearly larger than that of the device with the CdSe NPs due to the presence of ZnS shell, and was confirmed on the basis of the C-V results and the energy-band structures. This approach provides guidelines for optimizing the size and capping shell of the NPs for different electrical applications.

## REFERENCES

- R. J. Tseng, J. X. Huang, J. Ouyang, R. B. Kaner, and Y. Yang, *Nano Lett.* 5, 1077 (2005).

- 2. W. Lu and C. M. Lieber, Nat. Mater. 6, 841 (2007).

- 3. J. C. Scott and L. D. Bozano, Adv. Mater. 19, 1452 (2007).

- 4. Q. D. Ling, Y. Song, S. J. Ding, C. X. Zhu, D. S. H. Chan, D. L. Kwong, E. T. Kang, and K. G. Neoh, *Adv. Mater.* 17, 455 (2005).

- L. E. Hueso, I. Bergenti, A. Riminucci, Y. Q. Zhan, and V. Dediu, *Adv. Mater.* **19**, 2639 (2007).

- 6. M. N. Kozicki, C. Gopalan, M. Balakrishnan, and M. Mitkova, *IEEE Trans. Nanotechnol.* 5, 535 (2006).

- 7. S. H. Lee, Y. Jung, and R. Agarwal, *Nat. Nanotechnol.* 2, 626 (2007).

- 8. C.-H. Ji, I.-S. Oh, and S.-Y. Oh, *Electron. Mater. Lett.* 11, 795 (2015).

- 9. S. C. Yoon and I. C. Hwang, *Electron. Mater. Lett.* **11**, 41 (2015).

- M. H. White, D. A. Adams, and J. K. Bu, *IEEE Circuits Devices* 16, 22 (2000).

- 11. Y. L. Yang and M. H. White, *Solid-State Electron.* **44**, 949 (2000).

- 12. K. Kim and S. Y. Lee, Microelectron. Eng. 84, 1976 (2007).

- 13. J. S. Lee, C. S. Kang, Y. C. Shin, C. H. Lee, K. T. Park, J. S. Sel, V. Kim, B. I. Choe, J. S. Sim, J. Choi, and K. Kim, *Jpn. J. Appl. Phys. Part* 1, 45, 3213 (2006).

- E. Kapetanakis, P. Normand, D. Tsoukalas, K. Beltsios, J. Stoemenos, S. Zhang, and J. Van Den Berg, *Appl. Phys. Lett.* 77, 3450 (2000).

- C. Lee, J. H. Kwon, J. S. Lee, Y. M. Kim, Y. Choi, H. Shin, J. Lee, and B. H. Sohn, *Appl. Phys. Lett.* **91**, 153506 (2007).

- 16. C. J. Kim, S. W. Ryu, Y. K. Choi, J. J. Chang, S. H. Bae, and B. H. Sohn, *Appl. Phys. Lett.* **93**, 052106 (2008).

- D. Gupta, M. Anand, S. W. Ryu, Y. K. Choi, and S. H. Yoo, *Appl. Phys. Lett.* 93, 224106 (2008).

- 18. S. J. Kim, Y. S. Park, S. H. Lyu, and J. S. Lee, *Appl. Phys. Lett.* 96, 033302 (2010).

- S. M. Jung, H. J. Kim, B. J. Kim, Y. S. Kim, T. S. Yoon, and H. H. Lee, *Appl. Phys. Lett.* 97, 153302 (2010).

- 20. C. P. Collier, T. Vossmeyer, and J. R. Heath, *Annu. Rev. Phys. Chem.*, **49**, 371 (1998).

- 21. P. J. Thomas, G. U. Kulkami, and C. N. R. Rao, *Chem. Phys. Lett.* **321**, 163 (2000).

- 22. J. De Blauwe, IEEE Trans. Nanotechnol. 1, 72 (2002).

- 23. S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe, and K. Chan, *Appl. Phys. Lett.* 68, 1377 (1996).